STIT 2002-2003

# **EXAMEN AUTOMATIQUE : LOGIQUE COMBINATOIRE**

Durée: 3 h, calculatrice et documents interdits.

**Remarque**: la notation tiendra compte de <u>l'exactitude</u> des réponses et de la <u>qualité</u> de la rédaction. Vos résultats, longuement réfléchis sur brouillon, sont à donner sur les feuilles de réponses jointes en annexe.

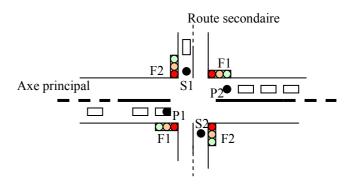

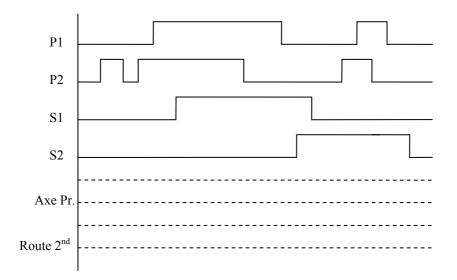

#### A. Fonctionnement de feux de croisement d'un carrefour

Des capteurs P1, P2, S1 et S2 détectant la présence de voitures ont été placés à l'intersection d'un carrefour d'un axe principal et d'une route secondaire. Ces capteurs donnent une information logique « 0 » quand il n'y a pas de voitures et « 1 » en présence de voitures. Les feux de circulation se trouvant à cette intersection sont commandés de la façon suivante :

Les feux F1 sont verts quand :

- il y a des voitures dans les deux voies de l'axe principal,

- il y a des voitures dans l'une des deux voies de l'axe principal sans qu'il y ait des voitures simultanément sur les deux voies de l'axe secondaire,

- il y a n'y a pas de voitures du tout

#### Les feux F2 sont verts quand:

- il y a des voitures dans l'une des deux voies ou les deux de la route secondaire et quand il y a au maximum une seule voie de l'axe principal occupée par des voitures

La priorité est donnée à l'axe principal quand il y a simultanément une voiture sur une des voies de l'axe principal et une voiture sur une des voies de la route secondaire.

On désire concevoir un circuit logique qui commande ces feux de circulation. Ce circuit possèdent 4 entrées (les capteurs) et 2 sorties (les feux). Une sortie est à l'état «1 » quand le feu doit être vert sinon elle est à «0 ».

- 1. Etablir la table de vérité de ce circuit logique.

- 2. Etablir les équations logiques (1<sup>ère</sup> forme canonique) des sorties.

- 3. Donner le câblage du circuit sous forme de logigrammes uniquement composé de portes NAND

- 4. Compléter le chronogramme

remarque : ces 4 réponses doivent être inscrites uniquement sur la feuille de réponse

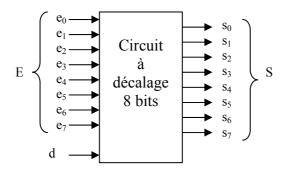

## B. Circuit à décalage 8 bits

On désire réaliser un circuit à décalage 8 bits.

En entrée du circuit, on place un mot binaire E codé sur 8 bits :  $E = (e_7 e_6 e_5 e_4 e_3 e_2 e_1 e_0)_2$ . On dispose d'une entrée supplémentaire d (direction) qui donne la direction du décalage : d=0 (décalage à gauche) et d=1 (décalage à droite). On récupère alors en sortie un mot binaire S de 8 bits :  $S = (s_7 s_6 s_5 s_4 s_3 s_2 s_1 s_0)_2$ . Le décalage se fait de la façon suivante :

- Lorsque d=0, on obtient en sortie l'entrée E décalée de 1 bit vers la gauche complétée à droite par un zéro : S = (e<sub>6</sub> e<sub>5</sub> e<sub>4</sub> e<sub>3</sub> e<sub>2</sub> e<sub>1</sub> a<sub>0</sub> 0)<sub>2</sub>

- Lorsque d=1, on obtient en sortie l'entrée E décalée de 1 bit vers la droite complétée à gauche par un zéro :  $S = (0 e_7 e_6 e_5 e_4 e_3 e_2 e_1)_2$

- 1. Donner l'équation de la sortie s<sub>0</sub> en fonction de d et des entrées e<sub>i</sub>

- 2. Donner l'équation de la sortie s<sub>7</sub> en fonction de d et des entrées e<sub>i</sub>

- 3. Donner l'équation des autres sorties s<sub>i</sub> (i= 1 à 6) en fonction de d et des entrées e<sub>i</sub>

- 4. Déduire un schéma de câblage de ce circuit en portes logiques.

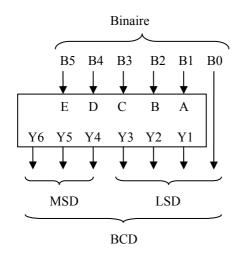

### C. Convertisseur Binaire → BCD

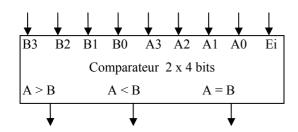

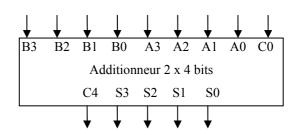

Le composant SN74185A est un convertisseur binaire 6 bits → BCD. Ne disposant pas de ce composant, on souhaiterait tout de même effectuer une conversion binaire→BCD. Seuls sont à notre disposition deux composants (cf. cours, si vous avez de la mémoire ③):

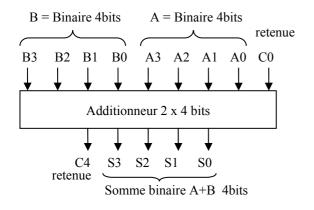

- un additionneur binaire 2x4 bits

- un comparateur binaire 2x4 bits

A l'aide de ces deux composants, réalisez un convertisseur 4 bits→BCD dont vous donnerez le câblage (complétez la feuille de réponses). On se souviendra ② que le passage du codage binaire naturel d'un nombre supérieur décimal > 9 se fait en ajoutant 6 au codage binaire pour obtenir le codage BCD correspondant.

#### NB: Les schémas des composants sont donnés en annexe.

## **Annexes**

LSD : Least Significative Digit MSD : Most Significative Digit BCD : Binary Coded Decimal

SN 74185A : Convertisseur binaire 6bit→BCD

$$B = Binaire 4bits$$

$$B3 B2 B1 B0 A3 A2 A1 A0 Ei$$

$$Comparateur 2 x 4 bits$$

$$A > B$$

$$S I E$$

$$Valide$$

$$A = Binaire 4bits$$

$$Valide$$

$$A = B$$

$Si Ei = 0 \quad et \quad \forall A, \ \forall B \quad alors \quad S = I = E = 0$   $Si Ei = 1 \quad alors$   $Si \ A < B \quad alors \quad S = 0 \quad I = 1 \quad E = 0$   $Si \ A > B \quad alors \quad S = 1 \quad I = 0 \quad E = 0$   $Si \ A = B \quad alors \quad S = 0 \quad I = 0 \quad E = 1$

| NOM: |  |  |

|------|--|--|

|------|--|--|

# Réponses de l'exercice A :

Table de vérité :

| P1 | P2 | S1 | S2 | F1 | F2 |  |

|----|----|----|----|----|----|--|

| 0  | 0  | 0  | 0  |    |    |  |

| 0  | 0  | 0  | 1  |    |    |  |

| 0  | 0  | 1  | 0  |    |    |  |

| 0  | 0  | 1  | 1  |    |    |  |

| 0  | 1  | 0  | 0  |    |    |  |

| 0  | 1  | 0  | 1  |    |    |  |

| 0  | 1  | 1  | 0  |    |    |  |

| 0  | 1  | 1  | 1  |    |    |  |

| 1  | 0  | 0  | 0  |    |    |  |

| 1  | 0  | 0  | 1  |    |    |  |

| 1  | 0  | 1  | 0  |    |    |  |

| 1  | 0  | 1  | 1  |    |    |  |

| 1  | 1  | 0  | 0  |    |    |  |

| 1  | 1  | 0  | 1  |    |    |  |

| 1  | 1  | 1  | 0  |    |    |  |

| 1  | 1  | 1  | 1  |    |    |  |

Fonctions:

## **Chronogramme:**

## Câblage:

# Réponses de l'exercice B :

$$S_0 =$$

$S_7 =$

$S_i =$

# Réponses de l'exercice C: